# ProSpeCT: Provably Secure Speculation for the Constant-Time Policy (Extended version)

Lesly-Ann Daniel, Marton Bognar, Job Noorman, Sébastien Bardin, Tamara Rezk, Frank Piessens

## ► To cite this version:

Lesly-Ann Daniel, Marton Bognar, Job Noorman, Sébastien Bardin, Tamara Rezk, et al.. ProSpeCT: Provably Secure Speculation for the Constant-Time Policy (Extended version). 32nd USENIX Security Symposium, USENIX Security 2023, Aug 2023, Anaheim (CA), United States. 10.48550/arXiv.2302.12108. hal-04479531

# HAL Id: hal-04479531 https://universite-paris-saclay.hal.science/hal-04479531

Submitted on 27 Feb 2024

**HAL** is a multi-disciplinary open access archive for the deposit and dissemination of scientific research documents, whether they are published or not. The documents may come from teaching and research institutions in France or abroad, or from public or private research centers. L'archive ouverte pluridisciplinaire **HAL**, est destinée au dépôt et à la diffusion de documents scientifiques de niveau recherche, publiés ou non, émanant des établissements d'enseignement et de recherche français ou étrangers, des laboratoires publics ou privés.

Distributed under a Creative Commons Attribution 4.0 International License

## **PROSPECT: Provably Secure Speculation for the Constant-Time Policy** (Extended version)

Lesly-Ann Daniel<sup>1</sup>, Marton Bognar<sup>1</sup>, Job Noorman<sup>1</sup>, Sébastien Bardin<sup>2</sup>, Tamara Rezk<sup>3</sup> and Frank Piessens<sup>1</sup>

<sup>1</sup>imec-DistriNet, KU Leuven, 3001 Leuven, Belgium <sup>2</sup>CEA, List, Université Paris Saclay, France <sup>3</sup>INRIA, Université Côte d'Azur, Sophia Antipolis, France

#### Abstract

We propose PROSPECT, a generic formal processor model providing provably secure speculation for the constant-time policy. For constant-time programs under a *non-speculative* semantics, PROSPECT guarantees that speculative and out-oforder execution cause no microarchitectural leaks. This guarantee is achieved by tracking secrets in the processor pipeline and ensuring that they do not influence the microarchitectural state during speculative execution. Our formalization covers a broad class of speculation mechanisms, generalizing prior work. As a result, our security proof covers all known Spectre attacks, including load value injection (LVI) attacks.

In addition to the formal model, we provide a prototype hardware implementation of PROSPECT on a RISC-V processor and show evidence of its low impact on hardware cost, performance, and required software changes. In particular, the experimental evaluation confirms our expectation that for a compliant constant-time binary, enabling ProSpeCT incurs no performance overhead.

#### 1 Introduction

It is well-understood that microarchitectural optimization techniques commonly used in processors can lead to security vulnerabilities [1]. One of the most recent and challenging problems in this space is the family of Spectre attacks [2], which abuse speculative execution to leak secrets to an attacker that can observe parts of the microarchitectural state of the platform on which the victim is executing.

In response to the discovery of Spectre, a wide range of countermeasures has already been proposed [3, 4, 5, 6, 7, 8, 9, 10, 11, 12, 13, 14, 15, 16, 17, 18, 19, 20]. It is an important and difficult challenge to understand the trade-offs offered by these mitigations in terms of security, performance, and applicability to legacy hardware or software.

On the one hand, software countermeasures targeting specific transient execution attacks can still leave other attacks unmitigated [21], and they must be patched every time new speculation mechanisms are introduced (e.g., the predictive store forwarding feature newly introduced in AMD Zen3 processors [22]). On the other hand, mainstream hardware mitigations have been recently shown ineffective [23] against Spectre-v2 (BTB) attacks [2].

Hardware-based secure speculation. In a recent paper, Guarnieri et al. [24] propose *hardware-software contracts* to compare hardware-based mechanisms for secure speculation and better understand how these defenses can enable software to provide end-to-end security guarantees. For instance, they show that certain types of hardware-level taint tracking [12, 16, 18] provide secure speculation for the *sandboxing* policy. On processors implementing one of these mechanisms, the software can simply enforce the sandboxing policy under a non-speculative semantics and does not need to consider the (error-prone and possibly expensive) placement of software speculation barriers.

However, none of the hardware defenses studied under the hardware-software contract framework enable secure speculation for the constant-time policy, except for completely disabling speculative execution. Hence, the classic cryptographic constant-time programming model [25] does not suffice to guarantee security on processors with these countermeasures, and significantly more complex and costly software programming models are required to recover security [21, 26, 27, 28, 29, 30, 31].

**Problem statement.** In this paper, we investigate how to provide efficient provably secure speculation for the constanttime policy under a wide range of speculation mechanisms. Specifically, we apply the hardware-software contract framework to another class of hardware taint-tracking mechanisms explicitly tracking *secrecy* of data in the microarchitecture (e.g., systems like ConTExT [32], SpectreGuard [33], or SPT [34]). In such systems, a constant-time program informs the processor about which memory cells contain secret data. Using this additional information, hardware-based tainttracking can provide *stronger* security guarantees than sandboxing approaches [24]. Additionally, we consider a wide variety of speculation mechanisms, whereas the model of Guarnieri et al. considers only speculation on conditional branches.

**Our proposal.** The main contribution of this paper is PROSPECT, a generic processor model formalizing the essence of such secrecy-tracking hardware mechanisms and a proof that it provides secure speculation for the constant-time policy. Specifically, off-the-shelf constant-time cryptographic libraries can be run securely on PROSPECT without additional protections for transient execution attacks.

PROSPECT is modular in the implementation of predictors and covers a broad class of speculation mechanisms, including branch prediction and store-to-load forwarding. As a novel aspect, PROSPECT additionally covers new mechanisms like predictive store forwarding [22] and even mechanisms that are not (yet) implemented in commercial processors, such as load value prediction [35] or value prediction [36]. In particular, we rigorously show that PROSPECT protects against Spectre-v2 (BTB) attacks [2], for which mainstream hardware mitigations have recently been shown ineffective [23]. As evidence for generality, we show that our mechanism even protects against Load Value Injection (LVI) attacks [37], which are particularly challenging to mitigate.

Another novel aspect of our formalization is the statement of our security condition, which allows a program to declassify a ciphertext while still requiring the processor to make sure that the attacker does not learn anything about the plaintext or the key used to compute the ciphertext.

To demonstrate the viability of our proposed mechanism, we extend a RISC-V processor to be PROSPECT-compliant and quantify the hardware costs. Results show that the overhead of PROSPECT in area usage and critical path is reasonable. We also demonstrate that the required software changes to cryptographic code are minimal and that the performance impact is negligible if secrets are precisely annotated. Our prototype is the first non-simulated hardware implementation of a speculative and out-of-order processor that implements secure speculation for the constant-time policy.

Contribution. In summary, our contributions are:

- We present PROSPECT, the first formal processor model providing provably secure speculation for the constanttime policy (Section 4). We propose a formal model of a processor that tracks secrets during execution and temporarily blocks speculative execution if secrets could leak. The model is generic; it supports a wide range of speculation mechanisms and formalizes the guarantees provided by prior hardware-based secrecy tracking mechanisms [32, 33, 34].

- We formally prove that PROSPECT provides secure speculation for the constant-time policy, i.e., programs that comply with the classic cryptographic constant-time discipline will not leak secrets through microarchitectural

channels (Theorem 1), including in the presence of declassification (Theorem 2). The proof holds for a large variety of speculation mechanisms, encompassing all known Spectre and LVI attacks.

- We are the first to consider load value speculation. Interestingly, our formal analysis reveals that executions resulting from *correct* load value speculation must sometimes be rolled-back to avoid attacks based on *implicit resolution-based channels* [18]. We prove this formally (Theorem 1) and provide an example in Section 4.6.

- We provide the first non-simulated hardware implementation of a processor offering secure speculation. We implement PROSPECT on a RISC-V processor supporting speculation (Section 6.1) and evaluate the costs of the proposed mechanism in terms of hardware, performance, and manual effort for precisely marking secret data (Section 6.2).

Availability. Our implementation and the experimental evaluation are open-sourced at https://github.com/proteus-core/prospect.

#### 2 Problem statement

#### 2.1 Transient execution attacks

Modern processors rely on heavy optimizations to improve performance. They can execute instructions out-of-order to avoid stalling the pipeline when the operands of an instruction are not available. Additionally, they employ *speculation* mechanisms to predict the instruction stream. The execution of instructions resulting from a misprediction, called *transient execution*, is reverted at the architectural level, but effects on the microarchitectural state (e.g., the cache) are persistent.

Spectre attacks [2] exploit these speculation mechanisms to force a victim to leak secrets during transient execution. An attacker can mistrain predictors to force a victim into transiently executing a sequence of instructions, called a Spectre gadget, chosen to encode secrets in the microarchitectural state. Finally, the attacker can use microarchitectural attacks to extract the secret. To this day, many variants of Spectre attacks have been discovered, exploiting a wide variety of speculation mechanisms [2, 3, 22, 38, 39, 40, 41].

Transient execution may also arise from incorrect data being forwarded by faulting instructions. For instance, on some processors, the result of unauthorized loads is transiently forwarded to subsequent instructions before the load is rolled back. This mechanism has first been exploited in Meltdownstyle attacks [42, 43] to exfiltrate secret data from another security domain. It is generally accepted that Meltdown-style attacks should be mitigated in hardware by preventing such forwarding from faulting loads. We consider Meltdown-style attacks out of scope for this paper. However, these faulting loads have also been exploited to *inject* incorrect data into the victim's transient execution, and, similarly to Spectre attacks, lead the victim to leak their secrets into the microarchitectural state. In particular, these so-called load value injection (LVI) attacks [37] are still possible in the presence of Meltdown mitigations zeroing out the results of faulting loads at the silicon level (i.e., LVI-NULL). LVI attacks are related to Spectre attacks that would exploit *value speculation* during loads.

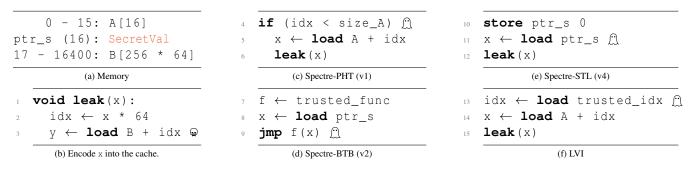

We illustrate variants of Spectre and LVI attacks in Listing 1, where programs in Listings 1c to 1e abuse different sources of transient execution (f) to encode SecretVal in the cache using the **leak** function in Listing 1b. After encoding, the attacker can extract the secret from the cache using cache attacks. Note that while we illustrate these attacks using a cache side-channel, transient execution vulnerabilities are independent of the microarchitectural side-channel they exploit, such as branch predictor state [44], SIMD units [45], port contention [46, 47], micro-op cache [48], etc. Consequently, the **leak** (x) function can be replaced with any other function that reveals information on the value of x via a timing or microarchitectural side-channel.

The **Spectre-PHT** (Pattern History Table) or Spectre-v1 variant [2] exploits the conditional branch predictor to transiently execute the wrong side of a conditional branch. For instance, in Listing 1c, an attacker can first mistrain the conditional branch predictor to take the branch and then call the piece of code with idx = 16 to make the victim transiently execute the branch, accessing SecretVal at line 5 and encoding it to the microarchitectural state at line 6.

The **Spectre-BTB** (Branch Target Buffer) or Spectre-v2 variant [2] exploits indirect branch prediction to transiently redirect the control flow to an attacker-chosen location. For example, the program in Listing 1d calls a trusted function, which performs secure computations using SecretVal. An attacker can mistrain the branch predictor such that, after line 9, the victim transiently jumps to the **leak** function instead of the trusted function and leaks SecretVal. The **Spectre-RSB** (Return Stack Buffer) variant [38, 39] is similar to Spectre-BTB but exploits target predictions for ret instructions.

The **Spectre-STL** (Store-To-Load-forwarding) or Spectrev4 variant [40] exploits the fact that load instructions can speculatively bypass preceding stores. In Listing 1e, the secret located at ptr\_s is overwritten at line 10, followed by a **load** to the same address, which should return 0. With Spectre-STL, the **load** may bypass the **store** at line 10 and transiently load **SecretVal**, which would then be leaked to the microarchitectural state at line 12.

Finally, **LVI** (Load Value Injection) attacks [37] exploit a faulting **load** to directly inject incorrect data into the victim's execution. For instance, in Listing 1f, an attacker can prepare the microarchitectural state so that the value 16 is forwarded to idx by the **load** instruction at line 13, hence accessing SecretVal at line 14 and leaking it at line 15.

#### 2.2 Secure speculation approaches

Since transient execution attacks were discovered, several studies have focused on adapting program semantics, security policies, and verification tools to take into account the *speculative semantics* of programs and place extra software-level protections against Spectre attacks, e.g., [21, 28, 29, 30, 31, 49, 50, 51, 52, 53, 54, 55, 56]. However, reasoning about transient execution attacks at the software level only can be burdensome and fragile. Firstly, it necessitates knowledge of microarchitectural details that are often not publicly available. Secondly, it requires changing security policies and applying software patches every time new speculation mechanisms are introduced (e.g., the predictive store forwarding feature newly introduced in AMD Zen3 processors [22]). Finally, software countermeasures targeting specific transient execution attacks can still leave the door open to other attacks [21].

Instead, we argue that, for a given policy *P*, enforcement mechanisms at the software level should only consider an architectural (non-speculative) semantics, while the hardware should guarantee that transient execution does not introduce additional vulnerabilities. We call this approach *hardware-based secure speculation for P*.

Hardware-based secure speculation for sandboxing. A sandboxing policy isolates a potentially malicious application by restricting the memory range it can access. A program is said to be *sandboxed* if it never accesses memory outside its authorized address range. Sandboxed programs are vulnerable to Spectre attacks, as out-of-bounds memory locations may still be accessed transiently and have their contents leaked to the microarchitectural state. As an example, the program in Listing 1c is sandboxed but can still access and leak out-of-bounds data when the condition is misspeculated.

Some hardware taint-tracking mechanisms [12, 16, 18] have been shown to enable secure speculation for sandboxing [24]. For instance, Speculative Taint Tracking (STT) [18] taints speculatively accessed data and prevents tainted values from being forwarded to instructions that may form a covert channel. In Listing 1c, STT taints the variable x at line 5 until the condition at line 4 is resolved. As x is tainted, its value is not forwarded to the insecure **load** in the **leak** function.

Unfortunately, hardware-based secure speculation for sandboxing *only protects speculatively accessed data*, meaning that secret data loaded in registers during sequential execution may still be transiently leaked. For instance, STT does not protect the program in Listing 1d against Spectre-BTB. At line 5, a secret is loaded during sequential execution. As a result, x is not tainted by STT, and its value can still be forwarded to an insecure instruction if the jmp is misspeculated. Hardware-based secure speculation for sandboxing is therefore insufficient to guarantee security for programs that compute on secrets, such as cryptographic primitives. To protect these programs, we need to enable hardware-based secure speculation for the constant-time policy.

Listing 1: Examples of code snippets vulnerable to transient execution attacks. The memory layout given in Listing 1a where SecretVal is the only secret input and ptr\_s = 16 is common to Listings 1c to 1f.  $\bigcirc$  indicates instructions triggering transient executions and  $\bigcirc$  indicates a leakage.

**Hardware-based secure speculation for constant-time.** A constant-time policy specifies that program secrets should not leak through timing or microarchitectural side channels. Before the advent of transient execution attacks, the constant-time policy was enforced with a coding discipline ensuring that the *control-flow of the program, addresses of memory accesses*, and *operands of variable-time instructions* do not depend on secret data. This coding discipline is the de facto standard for writing cryptographic code; it has been adopted in many cryptographic libraries [57, 58, 59, 60] and is supported by many tools, e.g., [25, 61, 62, 63, 64, 65, 66, 67, 68, 69, 70].

A standard definition for constant-time programs (i.e., programs adhering to the constant-time policy), and the one we use in this paper, is the following:

**Definition 1** (Constant-time program). A program is constanttime if the observation trace that it produces during *sequential execution* is independent of secret data (where the observation trace records the control flow and memory accesses).<sup>1</sup>

Unfortunately, adhering to this definition is insufficient to guarantee security on modern processors vulnerable to transient execution attacks like Spectre or LVI. Indeed, all programs in Listing 1 are constant-time according to Definition 1, but they are vulnerable to transient execution attacks.

Hardware-based countermeasures guaranteeing secure speculation for sandboxing do not guarantee secure speculation for the constant-time policy. Therefore, to enforce the constant-time policy on speculative processors, it is still necessary to insert specific protections (typically fence instructions or retpolines [5]) to protect against transient execution attacks. Software developers still have to reason about speculation when they want to enforce the constant-time policy. In this paper, we address the problem of *providing hardware-based provably secure speculation for the constant-time policy*.

#### **3** Informal overview of PROSPECT

In this section, we motivate our design choices, make explicit what guarantees have to be enforced by software, and sketch the requirements the hardware must enforce. Finally, we illustrate how PROSPECT protects the programs in Listing 1.

#### 3.1 Design choices

PROSPECT relies on a hardware-software co-design where developers annotate their secret data, and the hardware guarantees that no information about these secrets can leak during transient execution. The design of PROSPECT is motivated by two main objectives. The first objective is to support existing constant-time code with minimal software changes. To this end, we base our annotation and declassification mechanism on ConTExT [32] in which developers partition the memory into public and secret regions and can declassify secrets by writing them to public memory. The second objective is to support secure code while maintaining full performance benefits of speculative and out-of-order execution. Specifically, PROSPECT delays speculative execution only when a secret is about to be leaked; hence in constant-time programs (which do not leak secrets) PROSPECT only blocks mispredicted instructions.

**Software contracts.** Software developers must comply with three contracts:

Contract 1. Secret memory locations are labeled.

For instance, in Listing 1, address 16 is labeled as *secret* (or *high*), denoted H, whereas other addresses are labeled as *public* (or *low*), denoted L.

Contract 2. The program is constant-time.

**Contract 3.** Secret values written to public memory are *intentionally declassified* by the program.

Contract 3 allows, for instance, cryptographic code to declassify ciphertexts. However, software developers must make sure to not unintentionally declassify secrets by writing them to public memory.

<sup>&</sup>lt;sup>1</sup>We give a formal definition in Section 4.5. For simplicity, we do not include variable-time instructions in our security proofs but discuss how to handle them with PROSPECT.

We prove in Section 4.5 that if programs comply with these three contracts, then execution on PROSPECT does not leak secrets through timing and microarchitectural side channels.

**Hardware requirements.** On the hardware side, PROSPECT must realize the following:

**Requirement 1.** During the execution of a program, the processor tracks *security levels*. Concretely, it labels values loaded from memory with their corresponding security level (L or H) and soundly propagates these security levels during computations.

**Requirement 2.** The processor prevents values with security level H to be leaked during speculative execution. Hardware developers identify *insecure instructions* that may leak data through (1) changing the microarchitectural state, (2) influencing the program counter, or (3) exhibiting operand-dependent timing. The processor prevents these instructions from being speculatively executed with secret operands.

**Requirement 3.** Predictions do not leak secret data, in particular: (1) predictor states are only updated using public values, and (2) speculations are rolled back (even the *correct* ones) when their outcome depends on secrets (otherwise, it would leak whether the public prediction is equal to the secret value).

#### **3.2 PROSPECT through illustrative examples**

Consider the program in Listing 1c, assuming that idx = 16and the condition is misspeculated to *true*. When executing the **load** instruction at line 5, PROSPECT tags the register x with the security level corresponding to address 16, denoted  $x \mapsto (\texttt{SecretVal:H})$  (by Req. 1).<sup>2</sup> Then, when the **leak** function is executed, the **load** instruction (line 3, Listing 1b) is blocked because it would leak a secret-labeled value during speculative execution (by Req. 2). Conversely, if register x contains a public-labeled value, i.e.,  $x \mapsto (v:L)$ , the **load** instruction is not blocked. PROSPECT only blocks speculative execution in a few restricted cases, namely when secret data is about to be leaked.

Notice that, contrary to sandboxing-based approaches, PROSPECT also protects secrets loaded in architectural registers from being transiently leaked. For example, in Listing 1d, when the secret is loaded at line 8, x is labeled with H, which prevents the secret from being transiently leaked later (by Req. 2) if the **jmp** instruction at line 9 transiently jumps to the **leak** function.

So far, we have seen examples of PROSPECT applied to Spectre-PHT and Spectre-BTB (Spectre-RSB is similar to the latter). The protection generalizes to any other source of speculation, such as load value prediction (which encompasses LVI and Spectre-STL). Take, for instance, the program in Listing 1f. Here, the source of speculation is the **load** instruction, which transiently forwards an incorrect value at line 13. Until the **load** is resolved, PROSPECT considers the following instructions speculative. Consequently, (by Req. 2) it does not forward the secrets to the **load** in the **leak** function (Listing 1b, line 3) and prevents the LVI attack.

Finally, PROSPECT also guarantees (by Req. 3) that predicted values do not depend on secrets. In particular, secret values cannot be speculatively forwarded to other instructions. For example, in Listing 1e, the **load** instruction at line 11 cannot speculatively load SecretVal, because the corresponding address is labeled as secret. Notice that PROSPECT still allows forwarding public values.

#### 4 Formalization and theorems

This section presents one of the core contributions of this paper, the formalization of PROSPECT. The PROSPECT semantics builds on prior semantics [24], extended to consider a broader spectrum of prediction mechanisms. Moreover, it generalizes the standard constant-time leakage model; in addition to disclosing control-flow and memory accesses, our semantics also discloses *all public-labeled data*. Concretely, all public-labeled data can influence predictions and is observable by an attacker.

#### 4.1 ISA language

The ISA is modeled using a small assembly language called  $\mu$ ASM [29], described in Fig. 1.  $\mathcal{V}$  is a set of values, including memory addresses and program locations, and we let v and 1 range over  $\mathcal{V}$ . pc denotes the program counter register, and r, x denote registers with  $x \neq pc$ . A program *P* is a partial mapping from locations to instructions. We use *P*[1] to denote the instruction at location 1.

```

(Expressions) e ::= v | r | e_1 \otimes e_2

(Instructions) inst ::= x \leftarrow e | jmp e | beqz e l | x \leftarrow load e | store <math>e_a e_v

```

Figure 1: Syntax of  $\mu$ ASM programs where  $\otimes$  denotes a binary operation.

**Security levels.** We assume a lattice  $\Lambda$  with two security levels: public (low, L) and secret (high, H). We let  $\mathbf{s}, \mathbf{s}', \mathbf{s}_0, \ldots$  range over security levels from  $\Lambda$ .  $\Box$  denotes the least upper bound operation on the lattice, with  $L \sqcup H = H$ . Additionally, we let (v:s) denote a value v with security level s, ranging over the set  $\hat{\mathcal{V}} = \mathcal{V} \times \Lambda$ . For simplicity, we restrict our description to this 2-level security lattice, but this work generalizes to arbitrary security lattices.

<sup>&</sup>lt;sup>2</sup>A more conservative design choice, adopted by ConTExT [32], would be to prevent such speculative loads from accessing secret memory locations and to prevent the execution of line 5. However, we formally show that secure speculation is possible with this more liberal design choice.

**Location of secret data.** As stated in Contract 1, programmers annotate secret data in the code. In our formal semantics, we assume that they do so by specifying a *security memory partition*  $s_m$ , which maps memory addresses to security levels in  $\Lambda$ . We assume this mapping to be fixed, it cannot change over time. Hence, for the sake of readability, we do not explicitly include it in the configurations of the semantics rules.

#### 4.2 Hardware configurations

Hardware configurations are of the form  $\langle m, r, buf, \mu \rangle$ , where *m* is the memory, which maps addresses to values in  $\mathcal{V}$ ; *r* is the register map, which maps registers to pairs of a value and a security level in  $\hat{\mathcal{V}}$ ; *buf* is the reorder buffer, which is a sequence of (possibly transient) instructions; and  $\mu$  is the *microarchitectural context*.

**Microarchitectural context.** The microarchitectural context  $\mu$  can be thought of as the part of the microarchitectural state that the attacker controls. It is an abstract component that models both the *observations* that the attacker can make and the *influence* the attacker has on predictions and scheduling. Formally, it is a stateful deterministic component offering three functions:

- *update*, called by the semantics whenever microarchitectural state possibly leaks to the attacker;

- predict, giving the attacker control over predictions, for instance, to predict jump targets or load values;

- *next*, giving the attacker control over scheduling decisions that determine the next processor step to execute.

Hence, our definition of the semantics must make sure that for each computation step,  $\mu$  is updated with all information that could leak from that computation. In particular, updates should include the program counter and the addresses of memory accesses (which *directly* influence the instruction and data cache), but also operands of variable-time instructions (which do not directly influence the microarchitectural state, but might do so *indirectly* via timing variations [71]).

Importantly, to satisfy Req. 2 and 3, our evaluation rules must satisfy the following invariant: if the program is constanttime (as stated in Contract 2), secret data should never leak to  $\mu$ . In particular, the *update* function should never be given secret data as input during speculative execution. It follows from our security theorems that this is indeed the case.

**Reorder buffer.** In out-of-order processors, program instructions are fetched in order and placed in a *reorder buffer* (ROB) where they can be executed out-of-order. Contrary to ISA instructions, ROB instructions, defined in Fig. 2, keep track of the security levels of values. In addition, jmp and beqz are directly translated to pc assignments when they are fetched and thus are not part of ROB instructions. This also implies that, contrary to ISA instructions, assignments in the ROB can target pc. Finally, instructions in the ROB with predicted values are tagged with the address 1 of the instruction that the prediction resulted from; otherwise, they are tagged with  $\varepsilon$ .

(Tags)

$$T ::= 1 | \varepsilon$$

(ROB exp)  $e ::= (v:s) | r | e_1 \otimes e_2$

(ROB inst)  $i ::= r \leftarrow e@T | x \leftarrow load e@T$

**store**  $e_a e_v@T$

During the execution, changes that occur in the ROB are applied to the registers using the function *apl* [24]. When the value of an assignment in the reorder buffer is not resolved yet, the corresponding register is mapped to a special symbol  $\perp$ , meaning that it is undefined. Thus, the function *apl* generates a new register map where the value of some registers is undefined.

**Definition 2** (Apply function *apl*). For all register maps *r* and reorder buffers *buf*:

$\begin{array}{l} apl(\boldsymbol{\epsilon},r)=r\\ apl(\mathbf{r}\leftarrow(\mathbf{v}:\mathbf{s})@T\cdot buf,r)=apl(buf,r[\mathbf{r}\mapsto(\mathbf{v}:\mathbf{s})])\\ apl(\mathbf{r}\leftarrow e@T\cdot buf,r)=apl(buf,r[\mathbf{r}\mapsto\perp]) \text{ if } e\notin\hat{\mathcal{V}}\\ apl(\mathbf{x}\leftarrow \texttt{load}\ e@T\cdot buf,r)=apl(buf,r[\mathbf{x}\mapsto\perp])\\ apl(\ \texttt{store}\ e_a\ e_v@T\cdot buf,r)=apl(buf,r) \end{array}$

#### 4.3 Sanitization of secret values

An important feature of PROSPECT is the ability to *sanitize* secret values during speculative execution and predictions. To achieve sanitization, we define a low-projection for values denoted  $(v:s)|_{L}$ . It discloses public values but replaces secret values with  $\perp$ .

Definition 3 (Low-projection).

$$(v:L)|_{L} = (v:L)$$

$(v:H)|_{L} = \bot$   $\bot|_{L} = \bot$

We let  $r|_{L}$  be the point-wise extension of  $\cdot|_{L}$  to register maps. Hence, a sanitized register map  $r|_{L}$  maps registers to either their value when the associated security level is public or to  $\perp$  when the value is unresolved, or when it is secret.

**Definition 4** (Low memory projection). We define the lowprojection of a memory  $m|_{L}$  such that for all addresses a:

$$m|_{L}(a) = \begin{cases} m(a) & \text{if } s_{m}(a) = L \\ \bot & \text{otherwise} \end{cases}$$

The low-projection of a reorder buffer buf, denoted  $\lfloor buf \rfloor_L$ , discloses all low values in buf. Values with security level H are replaced by  $\bot$ . On the other hand, values with security level L, unresolved expressions, and tags are not replaced. Details are deferred to Appendix B.

Sanitizing secrets in speculative execution. We define a function *aplsan* that selectively sanitizes the register map returned by *apl*. In sequential execution (i.e., when no instruction in *buf* results from a prediction), it directly returns the result of *apl*. During speculative execution (i.e., where at least one instruction in *buf* results from a prediction), it returns the low-projection of *apl*, in which secrets are replaced with  $\perp$ .

**Definition 5** (Apply function  $aplsan(\cdot, \cdot)$ ).

$aplsan(buf,r) = \begin{cases} apl(buf,r) & \text{if } \forall inst @T \in buf. \ T = \varepsilon \\ apl(buf,r)|_{L} & \text{if } \exists inst @T \in buf. \ T \neq \varepsilon \end{cases}$

Concretely, the function *aplsan* is a crucial part of Req. 2; it acts as a filter that prevents forwarding secret data to insecure instructions (which *update* the microarchitectural context) during speculative execution.

#### 4.4 Evaluation rule

**Expression evaluation.** The evaluation of an expression *e* with a register map *r*, denoted  $\llbracket e \rrbracket_r$ , is a partial function from expressions to labeled values in  $\hat{\mathcal{V}}$ . It is undefined if one of the sub-expressions is undefined. Importantly, the evaluation of a binary operation propagates the security level of its operands in a conservative way (cf. Req. 1); if at least one of the operands has security level H, then the resulting security level is H. Details are available in Appendix B.

**Instruction evaluation.** The hardware semantics is given by a main relation  $c_1 \rightarrow c_2$  and an auxiliary relation  $c'_1 \rightarrow c'_2$  where  $c_1$  and  $c_2$  are hardware configurations and d is a directive. Leaks are highlighted in the rules and \_ is used to denote that there exists an expression, but this expression is not important in the context.

The directive determines which processor step to execute: the fetch directive fetches an instruction and places it at the end of the ROB, execute *i* executes the  $i^{\text{th}}$  instruction in the ROB, retire removes the oldest instruction from the ROB and commits its changes to the register map and memory.

The STEP rule selects the next directive to apply from the microarchitectural context using the function  $next(\mu)$  and updates the hardware configuration accordingly:

$$\frac{\mathsf{STEP}}{\mathsf{d} \triangleq \mathsf{next}(\mu')} \frac{\mu' \triangleq \mathsf{update}(m|_{\mathsf{L}}, r|_{\mathsf{L}}, \lfloor \mathsf{buf} \rfloor_{\mathsf{L}}, \mu)}{\langle m, r, \mathsf{buf}, \mu' \rangle \xrightarrow{d} \langle m', r', \mathsf{buf}', \mu'' \rangle} \frac{\mathsf{d} \triangleq \mathsf{next}(\mu')}{\langle m, r, \mathsf{buf}, \mu \rangle \rightarrow \langle m', r', \mathsf{buf}', \mu'' \rangle}$$

The rule updates the microarchitectural context using publiclabeled values from the memory  $m|_{L}$ , the register map  $r|_{L}$ , and the reorder buffer  $\lfloor buf \rfloor_{L}$ . This means that *any public-labeled* value can influence subsequent predictions. In Section 5, we show how this abstraction captures existing prediction mechanisms. It also means that any public-labeled value is leaked to the attacker, which effectively leaks *more* than the standard constant-time leakage model corresponding to Definition 1.

We present some evaluation rules for each directive, the full set of rules is available in Appendix B.

**Fetch directive.** The instructions are fetched in program order and placed in the ROB. We provide here the rule FETCH-PREDICT-BRANCH-JMP, which applies when the instruction to fetch is a branch or jump.

FETCH-PREDICT-BRANCH-JMP

$$(1:\_) \triangleq \llbracket pc \rrbracket_{apl(buf,r)}$$

$$\frac{P[1] \in \{ \text{ beqz } e\_, \text{ jmp } e \} \quad 1' \triangleq predict(\mu)}{\langle m, r, buf, \mu \rangle} \xrightarrow{\langle m, r, buf \cdot pc \leftarrow (1':L)@1, \mu \rangle}$$

The rule predicts the next program location 1' and updates pc in the ROB accordingly.<sup>3</sup> Notice that the next location 1' is added to the ROB with security level L, hence it will be leaked to the microarchitectural context in the next STEP rule. In the same way, the current location 1, added as a speculation tag in the ROB, is also leaked.

**Execute assignments.** The rule EXECUTE-ASSIGN evaluates an expression e and updates the value of a register r in the ROB accordingly. The rule EXECUTE-ASSIGN assumes that the evaluation of the expression e does not leak information about its operands—in particular, the execution time of the instruction is independent of the value of its operands. In this case, the instruction can securely execute using secret data. Therefore, the rule uses the non-sanitized register map apl(buf, r) to evaluate e (cf. the boxed hypothesis). For *variable-time (insecure) instructions* [72, 73, 74], we can simply replace the function apl(buf, r) in the box with the function apl(suf, r) to prevent the instruction from executing using secret data during speculative execution (cf. Req. 2).

EXECUTE-ASSIGN

$$\begin{array}{c} |buf| = i - 1 \qquad e \notin \hat{\mathcal{V}} \qquad inst = r \leftarrow e @T \\ \hline (\mathbf{v}:\mathbf{s}) \triangleq \llbracket e \rrbracket_{apl(buf,r)} \qquad inst' \triangleq r \leftarrow (\mathbf{v}:\mathbf{s}) @T \\ \hline \langle m, r, buf \cdot inst \cdot buf', \mu \rangle \xrightarrow[\text{execute } i]{}} \langle m, r, buf \cdot inst' \cdot buf', \mu \rangle \end{array}$$

**Execute loads.** The rule EXECUTE-LOAD-PREDICT predicts the value of a **load** instruction and updates the ROB with this predicted value. Note that the predicted value v is added to the ROB with security level L and is hence observable. This is consistent with the fact that predictions can only depend on public data (cf. Req. 3).

EXECUTE-LOAD-PREDICT

$$|buf| = i - 1$$

$$inst = x \leftarrow \mathbf{load} \ e @T \qquad (1:_) \triangleq [[pc]]_{apl(buf,r)}$$

$$\underline{v \triangleq predict(\mu)} \quad inst' \triangleq x \leftarrow (v:L) @1$$

$$\overline{\langle m, r, buf \cdot inst \cdot buf', \mu \rangle} \xrightarrow[execute i]{} \langle m, r, buf \cdot inst' \cdot buf', \mu \rangle$$

<sup>&</sup>lt;sup>3</sup>Note that what we call prediction here also covers store-to-load forwarding, load value prediction, and load value injection, as discussed in Section 5.

The rule EXECUTE-LOAD-COMMIT commits the result of a predicted **load** instruction to the ROB when the prediction is correct. It also leaks the address of the load to the microarchitectural context. The rule uses the *sanitized* value a of the address, which effectively prevents the rule to be applied during speculative execution when the address is secret (Req. 2). Additionally, notice that the rule can only be applied if the address a corresponds to public memory (i.e.,  $s_m(a) = L$ ). If the address a maps to secret memory (meaning that m(a) is secret), a rollback is performed to prevent leaking whether the secret value m(a) is equal to the predicted value v, as described in Req. 3 (a detailed example is provided in Section 4.6).

EXECUTE-LOAD-COMMIT

$$|buf| = i - 1 \quad inst = x \leftarrow (v:\_)@l_0$$

$$P[l_0] = x \leftarrow load \ e \quad store\_\_ \notin buf$$

$$(a:\_) \triangleq \llbracket e \rrbracket_{aplsan(buf,r)} \quad m(a) = v \quad s_m(a) = L$$

$$inst' = x \leftarrow (v:s_m(a))@e \quad \mu' \triangleq update(\mu, a)$$

$$\overline{\langle m, r, buf \cdot inst \cdot buf', \mu \rangle}_{execute \ i} \langle m, r, buf \cdot inst' \cdot buf', \mu' \rangle$$

The complementary rule EXECUTE-LOAD-ROLLBACK is applied when the prediction is incorrect or when m(a) is secret. It commits the correct value to the ROB and drops younger instructions from buf' (excluding the corresponding pc update).

Retire directives. Rules RETIRE-STORE-LOW and RETIRE-STORE-HIGH retire a store instruction on top of the ROB and update the memory accordingly. They also leak the address of the store to the microarchitectural context, following the constant-time leakage model. The rule RETIRE-STORE-LOW is evaluated if the address of the store corresponds to public memory (i.e.,  $s_m(a) = L$ ). In this case, regardless of its original security level, the value v becomes visible to the attacker: it is *declassified*. As stated in Contract 3, it is the responsibility of the developer to make sure that such declassification is intentional. In Section 4.6, we illustrate declassification in PROSPECT with an example. The declassified value is recorded above the evaluation relation, denoted  $\xrightarrow{v}$ . It does not affect the semantics but will be used in the theorems of Section 4.5. For secret store locations, the rule RETIRE-STORE-HIGH is applied, which produces an empty declassification trace.

$$\begin{array}{l} \text{RETIRE-STORE-LOW} \\ buf = \texttt{store} (\texttt{a:}) (\texttt{v:}) @ \varepsilon \cdot buf' \\ \mu' = update(\mu,\texttt{a}) \quad s_m(\texttt{a}) = \texttt{L} \\ \hline \langle m, r, buf, \mu \rangle \xrightarrow[\text{retire}]{v} \langle m[\texttt{a} \mapsto \texttt{v}], r, buf', \mu' \rangle \\ \end{array}$$

$$\begin{array}{l} \text{RETIRE-STORE-HIGH} \\ buf = \texttt{store} (\texttt{a:}) (\texttt{v:}) @ \varepsilon \cdot buf' \\ \mu' = update(\mu,\texttt{a}) \quad s_m(\texttt{a}) = \texttt{H} \\ \hline \langle m, r, buf, \mu \rangle \xrightarrow[\text{retire}]{\varepsilon} \langle m[\texttt{a} \mapsto \texttt{v}], r, buf', \mu' \rangle \end{array}$$

#### 4.5 Theorems

We first define a security theorem for PROSPECT that can be applied to constant-time programs without declassification, and then extend it to capture declassification. The full proofs are available in Appendix E.

An architectural configuration  $\alpha = \langle m, r \rangle$  is the subset of a hardware configuration, consisting of the memory and the register map. The (sequential) architectural semantics is given as a relation  $\alpha \xrightarrow[o]{\delta} \alpha'$ , which evaluates an architectural configuration  $\alpha$  to another architectural configuration  $\alpha'$ . It produces a sequence of observations *o* that contains the control flow (changes to the program counter) and the addresses of memory accesses. It also produces a declassification trace  $\delta$ , which is the sequence of all values written to public memory. Evaluation rules are otherwise standard and are provided in Appendix C.

Architectural configurations are said to be *low-equivalent*, written  $\alpha|_L = \alpha'|_L$ , if they are identical in the low-projections of their register maps and memories.

We let  $c_0 \xrightarrow{\delta} {}^n c_n$  denote an *n*-step execution from a hardware configuration  $c_0$  to a configuration  $c_n$ , which produces a *declassification trace*  $\delta$  (details in Appendix B). When  $\delta$  is not needed in the context, it is omitted. Similarly, we let  $\alpha_0 \xrightarrow{\delta}_{o} {}^n \alpha_n$  denote an *n*-step execution in the architectural semantics.

**Security for constant-time programs.** PROSPECT guarantees that if a program is constant-time (Contract 2) and does not declassify secret data (Contracts 1 and 3), then it does not leak secret data when running on PROSPECT.

The following definition formalizes the constant-time and no-declassification policy that we expect to be enforced on the software side. In that respect, it establishes a *hardwaresoftware security contract* [24].

**Definition 6** (Constant-time program). A program is constanttime if for any initial architectural configurations  $\alpha_0$  and  $\alpha'_0$ such that  $\alpha_0|_{\rm L} = \alpha'_0|_{\rm L}$ , and number of steps *n*:

$$\alpha_0 \stackrel{\delta}{\xrightarrow{o}}{}^n \alpha_n \implies \alpha'_0 \stackrel{\delta'}{\xrightarrow{o'}}{}^n \alpha'_n \land \stackrel{o}{=} o'$$

Additionally, if  $\delta = \delta'$  for all possible  $\alpha_0$  and  $\alpha'_0$ , we say that the program *does not declassify secret data*.

The goal of the attacker is to distinguish two low-equivalent initial configurations c and c', by providing a *strategy*, i.e., a concrete initial microarchitectural context  $\mu_0$  and implementations for *predict*, *update*, and *next* (designed by the attacker to distinguish the configurations). Under any such *deterministic* strategy, the attacker should have the same observations when running in c and c'.<sup>4</sup>

<sup>&</sup>lt;sup>4</sup>Note that nondeterministic strategies would produce different observations due to nondeterminism, not due to differences in secrets being leaked.

**Hypothesis 1.** The functions *predict*, *update*, and *next* are deterministic.

Under this hypothesis, the hardware semantics is deterministic.

The following theorem establishes end-to-end security for constant-time programs without declassification, running on PROSPECT.

**Theorem 1** (Security for constant-time programs.). For any constant-time program that does not declassify secret data, microarchitectural state  $\mu_0$ , initial configurations  $c_0 = \langle m_0, r_0, \varepsilon, \mu_0 \rangle$  and  $c'_0 = \langle m'_0, r'_0, \varepsilon, \mu_0 \rangle$  such that  $\langle m_0, r_0 \rangle|_{L} = \langle m'_0, r'_0 \rangle|_{L}$  and number of steps n,

$$c_0 \rightarrow^n c_n \implies c'_0 \rightarrow^n c'_n \land \mu_n = \mu'_n$$

where  $\mu_n$  and  $\mu'_n$  are the microarchitectural contexts in configurations  $c_n$  and  $c'_n$ , respectively.

Security with declassification. It is common for cryptographic programs to declassify ciphertexts after an encryption primitive. As we show in Appendix D, classic definitions of declassification [75, 76, 77, 78] allow a program to declassify more information than expected in the context of cryptographic code. Indeed, with such definitions, declassifying f (m) implicitly declassifies m when f is an injective function (e.g., a cryptographic permutation). In contrast, we propose a novel definition of security *up to* declassification that captures the following intuition: if a program only declassifies ciphertexts, then plaintexts and keys remain indistinguishable to an attacker (because they are *cryptographically* indistinguishable) and should not be leaked.

As described above, the declassification trace of an execution  $c \xrightarrow{\delta} {}^{n}c'$  is the sequence of all values stored to low (public) memory by the rule RETIRE-STORE-LOW. To express security up to declassification, we introduce a notion of patched *execution*, denoted  $(c, \delta) \hookrightarrow (c', \delta')$ , which replaces values stored to low-memory by values from a declassification trace  $\delta$  (usually obtained by a low-equivalent run in the standard semantics  $\rightarrow$  ). The patched execution ensures that the lowmemories of two low-equivalent executions remain equal, achieved by patching the second execution with the declassification trace of the first execution. For instance, a ciphertext that is declassified in the standard semantics can be used to patch another (low-equivalent) execution, to obtain two executions with the same declassified ciphertext (and to make sure that they leak the same values). Concretely, the patched execution only differs from the standard execution by the rule RETIRE-STORE-LOW, which is replaced by the following:

$\begin{array}{l} \text{RETIRE-STORE-PATCHED} \\ buf = \texttt{store} (\texttt{a:}_) (\texttt{v:}_) @\varepsilon \cdot buf' \\ \mu' = update(\mu,\texttt{a}) \quad \delta = \texttt{v}' \cdot \delta' \quad s_m(\texttt{a}) = \texttt{L} \\ \hline (\langle m, r, buf, \mu \rangle, \delta) \underset{\text{retire}}{\longrightarrow} (\langle m[\texttt{a} \mapsto \texttt{v}'], r, buf', \mu' \rangle, \delta') \end{array}$

We use  $(c, \delta) \hookrightarrow^n (c', \delta')$  to denote the evaluation of *n* steps in the patched execution. Similarly, we define a patched execution for the architectural semantics denoted  $(\alpha, \delta) \underset{o}{\longrightarrow} (\alpha', \delta')$ and provide the evaluation rules in Appendix C.

**Definition 7** (Constant-time up to declassification). A program is constant-time up to declassification if for any pair of initial architectural configurations  $\alpha_0$  and  $\alpha'_0$  such that  $\alpha_0|_{\rm L} = \alpha'_0|_{\rm L}$ , and number of steps *n*:

$$\alpha_0 \stackrel{\delta}{\underset{o}{\longrightarrow}}{}^n \alpha_n \implies (\alpha'_0, \delta) \stackrel{\sim}{\underset{o}{\longrightarrow}}{}^n (\alpha'_n, \varepsilon) \land \underset{o}{o} = o'$$

The following theorem establishes end-to-end security for constant-time programs up to declassification running on PROSPECT.

**Theorem 2.** For any constant-time program up to declassification, microarchitectural state  $\mu_0$ , initial configurations  $c_0 = \langle m_0, r_0, \varepsilon, \mu_0 \rangle$  and  $c'_0 = \langle m'_0, r'_0, \varepsilon, \mu_0 \rangle$  such that  $\langle m_0, r_0 \rangle|_{L} = \langle m'_0, r'_0 \rangle|_{L}$  and number of steps n,

$$c_0 \xrightarrow{\delta}{}^n c_n \implies (c'_0, \delta) \hookrightarrow^n (c'_n, \varepsilon) \land \mu_n = \mu'_n$$

where  $\mu_n$  and  $\mu'_n$  are the microarchitectural contexts in configurations  $c_n$  and  $c'_n$ , respectively.

In the next section, we provide an example to demonstrate how patched execution works.

#### 4.6 Examples

This section showcases key aspects of PROSPECT's semantics through small examples. Example 1 illustrates how declassification works and how PROSPECT prevents forwarding secrets to potential side channels during speculative execution. Example 2 demonstrates that when a predicted load value is resolved and the actual value is secret, speculative execution must be rolled back, even if the prediction was correct.

**Example 1** (Declassification). Consider an execution of the program in Listing 2 (in the standard hardware semantics  $\rightarrow$ ), where the register s evaluates to ( $s_1$ :H) in the initial configuration. Moreover, we assume that all conditions are predicted to be *true*, but only  $c_1$  can architecturally evaluate to *true*. Under this hypothesis, the program is constant-time up to declassification.

| 1 | <pre>store aL f(s) // Declassify f(s)</pre>                       |

|---|-------------------------------------------------------------------|

| 2 | $d \ \leftarrow \ \textbf{load} \ a_L$ // Load declassified value |

| 3 | if $c_1 \{ x \leftarrow load d \}$ // Allowed                     |

| 4 | if $c_2 \{ x \leftarrow load s \}$ // Blocked                     |

| 5 | if $c_3 \ \{ x \leftarrow \text{load } f(s) \ \} // Blocked$      |

Listing 2: Illustration of declassification where s is a secret input, f is a oneway function, and  $a_L$  is an address to a public memory location  $(s_m(a_L) = L)$ . For readability, **beqz** instructions are replaced with **if** constructs. At line 1, the program computes  $f(s_1)$  and declassifies the result by storing it to public memory. By the rule RETIRE-STORE-LOW, it also produces a declassification trace  $f(s_1)$ .

At line 2, the program loads the declassified value in register d. By the rule EXECUTE-LOAD-COMMIT, d has security level  $s_m(a_L) = L$ , hence PROSPECT can speculatively execute the **load** on line 3 to speed up computations before  $c_1$  is resolved. While it speculatively leaks d to the cache, it is not a security concern because the value has been intentionally declassified (cf. Contract 3).

Notice that because f is a one-way function, declassifying  $f(s_1)$  does not reveal information about  $s_1$ . In particular, the **load** on line 4 should certainly not be allowed to execute speculatively. PROSPECT faithfully enforces this policy; the rule EXECUTE-LOAD-COMMIT uses *aplsan* to compute the address of the load, and because this happens during speculative execution and s is labeled secret, we get  $[s]_{aplsan(buf,r)} = \bot$  (cf. Definitions 3 and 5). Hence, the **load** cannot be executed. Similarly, the **load** on line 5 is also blocked because the value f(s) is recomputed and inherits the secret label from s.

Now, to illustrate Theorem 2 (security up to declassification), consider a second execution of the program in the *patched semantics* starting with a configuration low-equivalent to the previous one, but where s evaluates to  $(s_2:H)$  and where declassified values are patched with the declassification trace of the first execution, i.e.,  $f(s_1)$ . According to Theorem 2, the leakage of the first execution and this second patched execution should be the same.

At line 1, the execution evaluates the rule RETIRE-STORE-LOW-PATCHED, which stores the value  $f(s_1)$  at address  $a_L$  (instead of storing  $f(s_2)$ ).

At line 2, the value  $f(s_1)$  is loaded into the register d and is assigned security level  $s_m(a_L) = L$ .

At line 3 (cf. rule EXECUTE-LOAD-COMMIT), the value of d can be forwarded to the **load** because its security level is L. Notice that because the second execution has been patched with the declassification trace of the first execution, the update to the microarchitectural context (i.e., the leakage) is the same in both executions.

At line 4, similarly to the first execution, PROSPECT does not forward the value of s to the **load** because its security level is H. By contrast, if we would consider an insecure microarchitecture that forwards the value, the microarchitectural context would be updated with  $s_1$  in the first execution and  $s_2$  in the second execution, which would violate Theorem 2.

Perhaps less intuitively, the leakage at line 5 would also be considered insecure w.r.t. Theorem 2, even though it is semantically equivalent to the leakage at line 3. Indeed, the leakage is not intentional w.r.t. Contract 3, which our security definition takes into account.

In summary, using the notion of *patched execution* allows us to express that there are no microarchitectural leaks beyond public information and explicitly declassified values. Even if some other secrets in the program are informationtheoretically derivable from declassified values (but, for instance, are cryptographically protected against such derivation), they should still be considered secret. In particular, our declassification condition guarantees that any attack exposing program secrets has to do so based on public information and explicitly declassified values and hence does not rely on any Spectre attack. We believe that for a cryptographic primitive, our definition of declassification can be composed with a standard notion of cryptographic indistinguishability to obtain a stronger notion of cryptographic indistinguishability for the execution of the primitive on PROSPECT.

**Example 2** (Rolling back a correct prediction). Consider the following program, where  $a_H$  is an address to a secret memory location ( $s_m(a_H) = H$ ):

```

1 x \leftarrow \text{load} a_H // \text{Load secret value}

2 y \leftarrow x + 4

```

We illustrate step-by-step a (possible) execution flow, focusing on the evolution of buf and highlighting changes at each step.

- Consider that the scheduler first fetches all instructions:  $buf = x \leftarrow load a_H @\varepsilon \cdot pc \leftarrow (2:L) @\varepsilon \cdot y \leftarrow x + 4@\varepsilon$

- The scheduler then applies the rule EXECUTE-LOAD-PREDICT and the predictor predicts the loaded value to be 0. Notice that the prediction is public, so we assume that the attacker knows (and can even influence) its value:  $buf = x \leftarrow 0@1 \cdot pc \leftarrow (2:L)@\varepsilon \cdot y \leftarrow x + 4@\varepsilon$

- Next, the scheduler applies the rule EXECUTE-ASSIGN, which computes y ← x + 4:

buf = x ← 0@1 · pc ← (2:L)@ε · y ← 4@ε

- When resolving the prediction, because we have s<sub>m</sub>(a<sub>H</sub>) = H, the rule EXECUTE-LOAD-COMMIT cannot be applied, and the execution is rolled back, even if the predicted value (0) was correct: buf<sub>rollback</sub> = x ← 0@ε·pc ← (2:L)@ε

Importantly, unconditionally rolling back the execution does not leak information about the secret value  $m(a_{\rm H})$ , whereas allowing EXECUTE-LOAD-COMMIT to proceed would leak whether  $m(a_{\rm H}) = 0$ . Indeed, if  $m(a_{\rm H}) \neq 0$ , then a rollback would happen, and the final ROB would be  $buf_{rollback}$ . If  $m(a_{\rm H}) = 0$ , the final ROB would be  $buf_{commit} = x \leftarrow 0@\varepsilon \cdot$  $pc \leftarrow (2:L)@\varepsilon \cdot y \leftarrow 4@\varepsilon$ .

Concretely, such a conditional rollback introduces a socalled *implicit resolution-based channel* [18]: the rollback case and the commit case lead to distinct timing behaviors (indeed, contrary to the commit case, the rollback case has to recompute the instructions following the load, which takes extra cycles). While prior solutions [18, 34] address implicit resolution-based channels (e.g., from memory disambiguation) by delaying the squashing of the implicit branch until prior speculations are resolved, this solution does not apply to load value prediction. Indeed, in our example, the implicit branch is already non-speculative (the processor knows for sure that the value can be committed).

#### **5** Discussion

This section discusses prediction mechanisms supported by PROSPECT, limitations, and compatibility with legacy code.

**Prediction mechanisms.** Prior work [18, 79] already stressed the importance of making predictions a function of public data. The novelty of PROSPECT is to allow predictions to depend on *any public data*, hence generalizing standard models of speculative execution. Indeed, public values are used in the STEP rule to update the microarchitectural context  $\mu$ , which is always given as an argument of *predict*. We now discuss how this model encompasses known prediction strategies.

Because the program counter is always public and therefore part of  $\mu$  (cf. Corollary 1 in Appendix E),  $predict(\mu)$ always has access to the current (and past) values of the program counter and corresponding instructions. Hence, it can make control-flow predictions based on the full control-flow history, which encompasses existing prediction strategies for conditional branches [80], indirect branches [81], and return targets.

Speculation on memory disambiguation, related to memory-disambiguation machine clears [41] (i.e., Speculative-store-bypass [40] and (predictive) storeto-load-forwarding [22]), is enabled by the rule EXECUTE-LOAD-PREDICT. However, PROSPECT forwards only *public values* from the memory and microarchitectural buffers (the store buffer in particular). This restriction could be lifted by propagating security levels in the store buffer and forwarding predicted values with their security level, as done by SPT [34]. We leave this optimization for future work.

Via the rule EXECUTE-LOAD-PREDICT, our semantics also encompasses the more futuristic load value prediction [35], which can be implemented as forwarding a simple constant or forwarding a value based on the *public* history of load operations. Value prediction [36] (also related to floatingpoint machine clears [41]), which we do not formalize here for simplicity, is similar to load value prediction. In particular, the prediction should not depend on secrets, and the execution must always be rolled back if the actual value is secret.

Finally, *predict* might also return any arbitrary value, which accounts for predictor states that have been poisoned by an attacker or that forward dummy values, hence encompassing Spectre, as well as LVI (and LVI-NULL) attacks.

**Limitations of PROSPECT.** Memory-ordering machine clears [41] are another source of transient execution, sometimes requiring rolling back memory operations to preserve

memory consistency for concurrent programs. Even though our semantics does not support concurrency, this kind of mechanism could be supported by tracking whether memory instructions might be rolled back w.r.t. to some memory consistency model, similar to speculations. For instance, to support the total-store-ordering model (TSO), the rule EXECUTE-LOAD-COMMIT should additionally make sure that all prior load operations in the ROB are resolved (e.g., with an additional hypothesis  $\_ \leftarrow load \_ \notin buf$ ).

Self-modifying code machine clears [41] can also cause transient execution in self-modifying code when the instruction cache (queried in the fetch stage) and the data cache (modified by prior **store** instructions) are desynchronized. Because our semantics assumes instruction memory to be fixed, it does not apply to self-modifying code.

Legacy software compatibility. PROSPECT is fully compatible with legacy software. Code without secret annotations works on PROSPECT as is, but without additional security over the base processor. Security and performance can also be traded off: the entire memory (or the stack) can be marked as secret, but it will likely result in additional performance overhead. Finally, to achieve security and optimal performance, only secret-handling code needs to be annotated. For instance, an annotated cryptosystem could be linked securely with (memory-safe) legacy code if the legacy code architecturally accesses only public or declassified information.

#### 6 Implementation and evaluation

#### 6.1 Implementation

To better understand the costs and benefits of PROSPECT, we built a prototype hardware implementation using the Proteus RISC-V processor framework.<sup>5</sup> Proteus is implemented in SpinalHDL [82], a Scala-based hardware description language (HDL). SpinalHDL generates Verilog or VHDL code that can be run in a simulator or synthesized for an FPGA.

From the many existing open-source RISC-V CPU implementations,<sup>6</sup> we selected Proteus because it is designed to be extended with new hardware mechanisms via a plugin system (inspired by VexRiscv [83]). It is easily configurable in the number of ROB entries and execution units, and it supports branch target prediction and speculative execution, making it vulnerable to Spectre-PHT, -BTB, and -RSB attacks.

PROSPECT is implemented as a Proteus plugin, with some additional modifications in the base processor. In future work, we are looking into combining PROSPECT with other security extensions on Proteus. Our implementation is open-sourced at https://github.com/proteus-core/prospect.

**Simplifications.** Our prototype adopts memory partitioning: secrets are co-located in one or more secret memory regions,

<sup>&</sup>lt;sup>5</sup>https://github.com/proteus-core/proteus

<sup>&</sup>lt;sup>6</sup>https://github.com/riscv/riscv-isa-manual/blob/master/ marchid.md

and we manually inform the hardware of the region boundaries. While it is possible to hardcode the boundaries of arbitrary secret regions in hardware, we implemented a more flexible approach that enables the configuration of secret region boundaries via control and status registers (CSRs). The number of CSRs can affect the hardware costs of the implementation; we report on setups allowing one and two secret regions. Note that in our benchmarks, we could co-locate all secrets in a single region when the stack is public and in two regions when the stack is secret. In future work, we plan to develop compiler support for co-locating all secrets in a single region and automatically setting up the secret region boundaries through CSRs.

The prototype takes a conservative approach and stalls every speculative instruction operating on secret data, not only *insecure instructions* (cf. Req. 2). Finally, interrupts are not supported.

**Code size.** The full implementation of a PROSPECT-enabled processor consists of 5275 lines of SpinalHDL code, which generates approximately 104,000 lines of Verilog code. The PROSPECT plugin is written in 90 lines of SpinalHDL, and approximately 270 additional lines of the base Proteus code were modified. For our evaluation, we use 5 execution units and a reorder buffer of size 16. To encourage further experimentation with different configurations, we open-source our evaluation setup.

#### 6.2 Evaluation

The security benefit of PROSPECT comes with a tradeoff in three different aspects:

- 1. *Hardware cost*: PROSPECT uses additional hardware to track secret data and restrict its propagation. This can have an impact on hardware cost metrics like area used and critical path.

- 2. *Runtime overhead*: PROSPECT can delay the forwarding of secret data, which might impact the execution time of applications.

- 3. *Labeling of secrets*: Software needs to declare what data is secret, possibly requiring additional developer effort to avoid unintentional declassification (cf. Contract 3).

To validate the security claims of the implementation [84], we executed code samples vulnerable against Spectre on both the base Proteus and the PROSPECT-extended implementation and did not observe leakage in the latter case.

Hardware cost. To assess the overhead of the area used and the critical path, we synthesized Proteus without and with the PROSPECT modifications for an Artix-7 XC7A35T FPGA with a speed grade of -1 using Xilinx Vivado. Our experiments showed a reasonable overhead for PROSPECT. The version supporting a single secret region increases the number of slice LUTs from 16,847 to 19,728 (+17%) and slice registers from 11,913 to 12,600 (+6%). The critical path increases from 30.1 ns to 30.7 ns (+2%). We did not observe any additional increase in these numbers when adding a second set of CSRs to support a second secret region.

**Runtime overhead.** The runtime overhead of PROSPECT depends on two main factors. First, the amount of data marked as secret: if a program only accesses public data, PROSPECT incurs no overhead, while if the whole memory is marked as secret, the overhead is maximal. Second, the performance benefit of speculative execution on the program: if the performance of a program heavily benefits from speculative execution, the overhead of PROSPECT will be higher than if the program does not benefit from speculative execution.

Making a binary PROSPECT-compliant requires colocating secrets in memory, which could impact performance, e.g. via caching effects. We leave an evaluation of these secondary effects for future work.

Configuring the secret regions from software using CSRs only requires a few additional instructions (loading the boundary addresses into the CSRs before starting the program), resulting in negligible overhead.

We evaluate the first two main factors using the synthetic benchmarks from SpectreGuard [33]. These benchmarks simulate a mix of computations on public data (whose performance heavily benefits from speculative execution) and an encryption routine (whose performance benefits less from speculative execution) with different fractions of speculation/crypto (i.e., **S/C**). We modify the benchmarks in two ways: (1) because we specifically target constant-time code, we replace the non-constant-time AES primitive with the constant-time chacha20 primitive from HACL\* [58], (2) we annotate not only the key and plaintext as secret but also all variables that may contain secrets to avoid unintentional declassification (cf. Contract 3).

We ran the benchmarks in three different configurations: the base processor with no PROSPECT extension (our baseline), precisely defining the secret region and defining a secret region to cover the entire address space. More precisely, for the second configuration, P(key), we co-locate all secrets in a single region and load the boundaries of this secret region into the CSRs. In the third configuration, P(all), we load the first and last address of the memory into the CSRs, protecting the entire address space. Results are given in Table 1, where the percentages denote the relative execution time compared to the baseline for each configuration.

In line with our expectations, our results show that for a PROSPECT-compliant binary, enabling the defense incurs no runtime overhead when secret values are only accessed in constant-time code. When marking the whole memory secret, the overhead ranges from 10% to 45%, which is comparable (but lower) to the overhead of SpectreGuard [33] when

Table 1: Relative SpectreGuard benchmark performance on PROSPECT.

| Setting  | 25 <b>S</b> /75 <b>C</b> | 50 <b>S</b> /50 <b>C</b> | 75 <b>S</b> /25 <b>C</b> | 90 <b>S</b> /10 <b>C</b> |

|----------|--------------------------|--------------------------|--------------------------|--------------------------|

| baseline | 100%                     | 100%                     | 100%                     | 100%                     |

| P(key)   | 100%                     | 100%                     | 100%                     | 100%                     |

| P(all)   | 110%                     | 125%                     | 136%                     | 145%                     |

enabled for the entire address space.<sup>7</sup> Overall, we conclude that PROSPECT incurs a low overhead when secret data is precisely annotated, especially for programs where only a restricted part of the code computes on secrets, which is a common scenario [32, 33] (in SSH clients, web servers, etc.). **Labeling of secrets.** To benefit from the security guarantees provided by our security theorems, code must be verified to be constant-time in the sequential execution model. Fortunately, verified constant-time implementations of cryptographic prim-

verified constant-time implementations of cryptographic primitives are readily available [58], and such verified code also makes explicit what program data should be marked as secret. However, it is still not trivial to identify which memory addresses should be marked as secret. For instance, if the compiler spills secret arguments on the stack, that stack memory must also be marked as secret to avoid unintentional declassification and comply with Contract 3. While it is secure to conservatively over-approximate the memory areas marked as secret (and, for instance, always mark the stack as secret), this has a performance cost.

Hence, we evaluate how difficult it is to obtain precise information about which memory addresses should be labeled secret for a set of representative constant-time cryptographic primitives given in Table 2. To do so, we manually annotate (in the C code) all local variables that may contain secret data, to place them in a dedicated memory section. Additionally, we patch the generated assembly code to clear secret values from registers after declassification. The number of required annotations and assembly lines is reported in Table 2. As a sanity check, we validate that secret data is not written by the compiler to public memory locations outside of the dedicated declassification memory.<sup>8</sup> In the worst case, the time required to annotate secret variables and to validate that no secrets are written on the stack was less than 1 hour.

Interestingly, in 3 of the 4 cryptographic primitives, secret registers are not spilled on the stack by the primitive itself but by the surrounding code. Therefore, for these examples, it is possible to isolate secrets from public data and *keep the stack public* to minimize performance impact.

Finally, for the more complex primitive curve25519, secret register spilling cannot easily be avoided manually. Hence, we label the stack as secret, and instead of annotating secret variables, we annotate *public* variables to place them

Table 2: Cryptographic primitives used for the experimental evaluation, reporting the lines of C code (LoC), whether the stack (S) is labeled public (L) or secret (H), the number of annotations manually  $(A_m)$ , and automatically  $(A_a)$  inserted for marking variables, and the number of assembly instructions (*I*) manually inserted.

|                             | LoC  | S | $A_m$ | $A_a$ | Ι | Description        |

|-----------------------------|------|---|-------|-------|---|--------------------|

| djbsort [ <mark>85</mark> ] | 246  | L | 3     | 0     | 6 | Constant-time sort |

| sha256 <b>[58]</b>          | 1795 | L | 34    | 0     | 6 | Hash function      |

| chacha20 <b>[58]</b>        | 1864 | L | 51    | 0     | 6 | Encryption         |

| curve25519 <b>[58]</b>      | 3026 | Η | 9     | 67    | 0 | Elliptic curve     |

out of the stack and limit the performance impact. Notice that because the program is constant-time, pointers are public and we can automate their annotation in 67 cases.

In summary, with reasonable manual effort, we were able to keep the stack public for 3 out of 4 cryptographic primitives and isolate public variables from the (secret) stack for the remaining primitive. We expect that this manual effort can easily be automated with compiler support along the lines of existing work for x86 [32, 86].

#### 7 Related work and conclusion

We discussed transient execution attacks throughout the paper, more details can be found in existing surveys [3, 41].

**Formal microarchitectural semantics.** Many studies have proposed operational semantics for speculative execution to formally reason about Spectre attacks (see [87] for a detailed comparison up to 2021). Most previous semantics only capture Spectre-PHT, with a few capturing other variants such as Spectre-STL [21, 27, 28, 88, 89], Spectre-BTB, and Spectre-RSB [27, 28]. Contrary to previous operational semantics, PROSPECT handles *arbitrary* load value prediction [35] and can additionally capture LVI [37]. Using *axiomatic semantics*, Ponce-de-León and Kinder [90] can accommodate new leakage models for different prediction mechanisms and thus cover such cases. In contrast to our work, they can also model attacks based on memory-ordering machine clears [41]. Yet, it is an open question how to model non-interference and declassification, as in our work, using axiomatic semantics.

**Declassification definitions.** Existing leakage models for secure speculation do not permit any kind of leakage [87] that depends on secrets. Yet, in practice, it is common to treat encrypted secrets as observable. In the literature before transient execution attacks, security properties with intentional leakage (i.e., declassification) have been widely studied [91]. When declassifying ciphertexts is a goal, declassification definitions that are not built for this, such as delimited release [76], may consider programs that unintentionally leak secrets (including the cryptographic keys), as secure, as we show in Appendix D. Our definition does not suffer from this limitation and is closer to cryptographically masked flows [92] since it

<sup>&</sup>lt;sup>7</sup>Of course, no direct comparison can be made as the compiled programs, architectures, and microarchitectures are different.

<sup>&</sup>lt;sup>8</sup>We track whether secret data is written to non-secret locations using a hardware plugin that we built on top of PROSPECT.

considers a symbolic model for declassified values. Laud [93] pioneered work in the area of security conditions composable with indistinguishability properties of encryption, which was later generalized to other cryptographic primitives [94, 95]. Later, Laud [96] devised necessary conditions to compose cryptographically masked flows with standard cryptographic indistinguishability properties. We stipulate that our security property will require similar conditions to compose. None of these previous works consider transient execution attacks.

Hardware defenses against Spectre. Many defenses specifically target the cache hierarchy [9, 10, 13, 14, 15, 17, 20, 97, 98, 99], yet, these defenses are still vulnerable to attacks exploiting other side channels [44, 45, 46, 47, 48].

Speculative taint-tracking approaches [12, 16, 18, 79] delay instructions that depend on speculatively loaded data. As shown in [24], these approaches enforce hardware-based secure speculation for sandboxing, but offer no protection for non-speculatively accessed data. Hence, they do not provide secure speculation for the constant-time policy.

DOLMA [100] additionally protects non-speculatively accessed data during speculation, but its performance relies on optimizations allowing (under certain conditions) speculative execution of variable-time instructions and memory operations, which might still be exploited via resource contention.

Data oblivious ISA extensions (OISA) [101] are a hardware-based secrecy-tracking mechanism that prevents secret data from leaking, *including during non-speculative execution*. Software must be updated to use the ISA extensions to make sure that secret data is not used as an unsafe operand. In contrast, PROSPECT can be retrofitted into existing ISAs and supports existing (constant-time) cryptographic code with minimal (software and hardware) changes.